CPLD芯片ICD2053B的原理構(gòu)造及其在數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

引言

在當(dāng)今數(shù)字化、智能化的工業(yè)控制和信息處理領(lǐng)域,數(shù)據(jù)采集系統(tǒng)扮演著至關(guān)重要的角色,它作為連接物理世界與數(shù)字世界的橋梁,負(fù)責(zé)實(shí)時(shí)、準(zhǔn)確地獲取各類傳感器和外部設(shè)備的信息。而復(fù)雜可編程邏輯器件(CPLD)以其高度的靈活性、強(qiáng)大的邏輯處理能力和可靠的時(shí)序性能,成為實(shí)現(xiàn)高效、穩(wěn)定數(shù)據(jù)采集邏輯控制的核心器件之一。ICD2053B作為一款典型的CPLD芯片,其獨(dú)特的原理構(gòu)造使其在數(shù)據(jù)采集應(yīng)用中展現(xiàn)出顯著優(yōu)勢。

一、CPLD芯片ICD2053B的基本原理與內(nèi)部構(gòu)造

CPLD(Complex Programmable Logic Device)是一種基于乘積項(xiàng)(Product-Term)結(jié)構(gòu)、集成度較高的可編程邏輯器件。ICD2053B作為其中一員,其內(nèi)部構(gòu)造核心在于實(shí)現(xiàn)靈活的數(shù)字邏輯功能。

- 基本架構(gòu):

- 宏單元(Macrocell):這是CPLD的基本邏輯單元。ICD2053B內(nèi)部包含數(shù)百個(gè)宏單元,每個(gè)宏單元通常由一個(gè)可編程的與陣列(實(shí)現(xiàn)組合邏輯)、一個(gè)觸發(fā)器(實(shí)現(xiàn)時(shí)序邏輯)以及選擇器(用于配置輸出路徑和反饋路徑)構(gòu)成。宏單元是實(shí)現(xiàn)具體邏輯功能(如計(jì)數(shù)器、狀態(tài)機(jī)、譯碼器)的基礎(chǔ)。

- 可編程互連陣列(PIA):這是CPLD架構(gòu)的關(guān)鍵。它是一個(gè)全局性的、可編程的布線資源池,將所有宏單元的輸入和輸出連接起來。通過PIA,任何一個(gè)宏單元的輸出可以靈活地路由到幾乎任何一個(gè)宏單元的輸入,從而實(shí)現(xiàn)了高度復(fù)雜邏輯電路的內(nèi)部連接,確保了信號的靈活布通和時(shí)序的一致性。

- 輸入/輸出單元(I/O Block):負(fù)責(zé)芯片與外部電路的接口。每個(gè)I/O引腳都可以被獨(dú)立配置為輸入、輸出或雙向端口,并可以設(shè)置輸出驅(qū)動能力、上拉/下拉電阻、電壓標(biāo)準(zhǔn)(如3.3V LVTTL)等,使其能夠直接連接各種傳感器、ADC(模數(shù)轉(zhuǎn)換器)、存儲器或微處理器。

- JTAG編程接口:用于芯片的邏輯功能配置(編程)和在系統(tǒng)測試,支持ISP(在系統(tǒng)編程)功能,便于系統(tǒng)升級和維護(hù)。

- 工作原理:用戶使用硬件描述語言(如VHDL或Verilog)描述所需的數(shù)字邏輯功能,通過開發(fā)軟件進(jìn)行綜合、布局布線,生成一個(gè)包含邏輯與互連信息的編程文件(如JEDEC文件)。將該文件通過JTAG接口下載到ICD2053B中,即可配置其內(nèi)部的與陣列、宏單元功能及PIA的連接關(guān)系,使其“變身”為特定的數(shù)字電路系統(tǒng)。一旦編程,配置信息通常存儲在非易失性存儲器(如EEPROM或Flash)中,上電即運(yùn)行,無需外部配置芯片。

二、ICD2053B在數(shù)據(jù)采集系統(tǒng)中的應(yīng)用優(yōu)勢

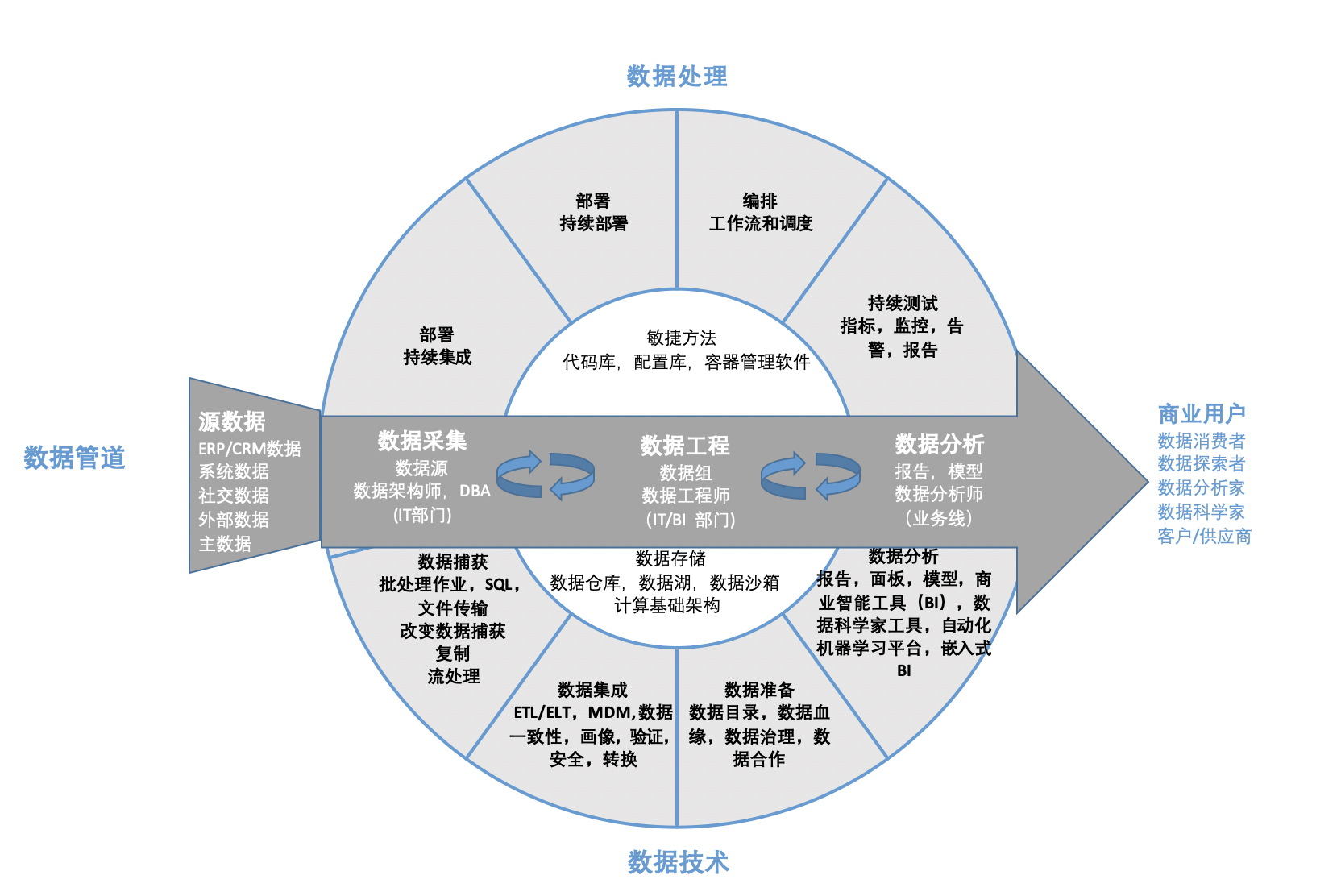

在數(shù)據(jù)采集系統(tǒng)中,ICD2053B主要扮演“智能接口”和“邏輯控制中樞”的角色,其應(yīng)用優(yōu)勢體現(xiàn)在:

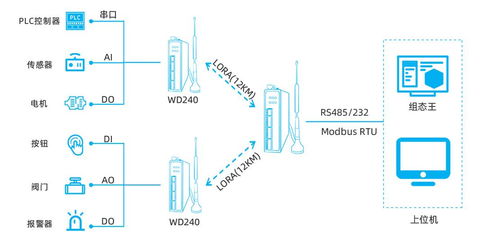

- 高度集成的接口邏輯控制:數(shù)據(jù)采集系統(tǒng)通常需要連接多種傳感器(模擬/數(shù)字)、ADC芯片、存儲器(FIFO、RAM)以及上位機(jī)(如通過UART、SPI、并行總線)。ICD2053B可以集成所有這些接口的控制邏輯,例如:

- ADC控制:產(chǎn)生精確的ADC啟動轉(zhuǎn)換信號、讀取轉(zhuǎn)換完成標(biāo)志、并按照特定時(shí)序讀取轉(zhuǎn)換結(jié)果數(shù)據(jù)。

- 通信協(xié)議實(shí)現(xiàn):高效實(shí)現(xiàn)SPI、I2C、UART、自定義并行總線等通信協(xié)議,完成與傳感器或主處理器的數(shù)據(jù)交換。

- 多路復(fù)用與通道管理:控制多路模擬開關(guān),實(shí)現(xiàn)多路傳感器信號的巡回采集。

- 精確的時(shí)序生成與管理:數(shù)據(jù)采集對時(shí)序要求極為嚴(yán)格。CPLD基于硬件并行處理,能夠生成納秒級精度的時(shí)鐘、使能、片選等控制信號,確保ADC采樣、數(shù)據(jù)鎖存、傳輸?shù)雀鳝h(huán)節(jié)嚴(yán)格同步,避免軟件控制可能帶來的時(shí)序抖動和不確定性。

- 數(shù)據(jù)預(yù)處理與緩沖:在將數(shù)據(jù)發(fā)送給主處理器(如MCU、DSP)之前,ICD2053B可以進(jìn)行初步的數(shù)據(jù)處理,如:

- 數(shù)字濾波:實(shí)現(xiàn)簡單的均值濾波、去抖動等算法。

- 格式轉(zhuǎn)換:將ADC的原始數(shù)據(jù)轉(zhuǎn)換為工程單位值,或進(jìn)行字節(jié)序重組。

- 數(shù)據(jù)打包與緩存:將多通道數(shù)據(jù)打包成特定幀格式,并存入片內(nèi)邏輯實(shí)現(xiàn)的FIFO緩沖區(qū),以匹配主處理器較慢的讀取速度,實(shí)現(xiàn)數(shù)據(jù)流的平滑。

- 可靠性高,響應(yīng)迅速:作為硬件邏輯執(zhí)行,不受軟件跑飛、中斷延遲等問題影響,系統(tǒng)抗干擾能力強(qiáng),對關(guān)鍵事件的響應(yīng)是確定且即時(shí)(微秒甚至納秒級)的。

- 設(shè)計(jì)靈活,易于修改:當(dāng)采集需求變化(如增加通道、改變通信協(xié)議、調(diào)整采樣率)時(shí),只需修改HDL代碼并重新編程CPLD,無需改變PCB硬件,極大縮短了開發(fā)周期和降低了升級成本。

三、典型應(yīng)用實(shí)例分析

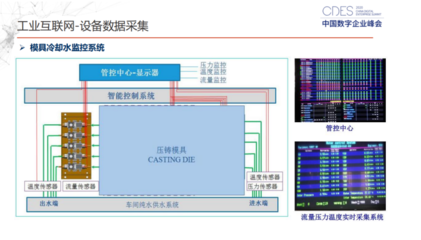

假設(shè)一個(gè)工業(yè)現(xiàn)場多通道溫度、壓力數(shù)據(jù)采集系統(tǒng):

- 系統(tǒng)構(gòu)成:多路熱電偶/RTD(通過信號調(diào)理電路)、多路壓力傳感器、高精度多通道ADC芯片、微處理器(MCU)、ICD2053B CPLD、通信模塊。

- ICD2053B的核心功能實(shí)現(xiàn):

- 邏輯控制核心:CPLD內(nèi)部構(gòu)建一個(gè)主狀態(tài)機(jī),協(xié)調(diào)整個(gè)采集流程。

- 通道掃描控制:按預(yù)設(shè)順序,循環(huán)輸出通道選擇信號至模擬多路開關(guān)。

- ADC驅(qū)動:為選中的通道產(chǎn)生精確的ADC啟動轉(zhuǎn)換脈沖,監(jiān)測轉(zhuǎn)換結(jié)束信號,并在恰當(dāng)時(shí)鐘沿讀取ADC輸出數(shù)據(jù)。

- 數(shù)據(jù)預(yù)處理:對讀取的原始數(shù)據(jù)進(jìn)行查表線性化補(bǔ)償(針對熱電偶)、或簡單的標(biāo)度變換。

- 數(shù)據(jù)緩沖與接口:將處理后的通道數(shù)據(jù)與通道號打包,寫入一個(gè)異步FIFO。實(shí)現(xiàn)一個(gè)SPI或并行總線接口邏輯,響應(yīng)MCU的讀取請求,將FIFO中的數(shù)據(jù)高效、無誤地傳輸給MCU進(jìn)行進(jìn)一步處理或上傳。

- 看門狗與異常處理:可集成硬件看門狗邏輯,監(jiān)控采集流程,在超時(shí)或異常時(shí)產(chǎn)生復(fù)位或中斷信號。

通過上述設(shè)計(jì),MCU得以從繁瑣、高實(shí)時(shí)的底層時(shí)序控制中解放出來,專注于更高層的任務(wù)調(diào)度、算法處理和人機(jī)交互,整個(gè)系統(tǒng)的可靠性、實(shí)時(shí)性和效率都得到顯著提升。

結(jié)論

CPLD芯片ICD2053B憑借其基于乘積項(xiàng)和全局互連陣列的確定性硬件結(jié)構(gòu),提供了高度靈活、可靠且高速的數(shù)字邏輯實(shí)現(xiàn)平臺。在數(shù)據(jù)采集系統(tǒng)中,它將分散的接口控制、精確的時(shí)序管理、初步的數(shù)據(jù)處理等功能集成于單一芯片,不僅簡化了系統(tǒng)硬件設(shè)計(jì),更大幅提升了數(shù)據(jù)采集的實(shí)時(shí)性、同步性和整體可靠性。隨著數(shù)據(jù)采集系統(tǒng)向更高速度、更多通道、更復(fù)雜預(yù)處理的方向發(fā)展,像ICD2053B這樣的CPLD將繼續(xù)發(fā)揮其不可替代的核心作用。

如若轉(zhuǎn)載,請注明出處:http://www.2weima.cn/product/58.html

更新時(shí)間:2026-02-21 14:59:28